英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

单芯片RF前端的数字声音录制广播

索尼半导体网络公司

索尼移动网络公司

索尼核心技术与网络公司

索尼数字通信网络公司

摘要:

一个完整的基于单芯片射频前端的数字声音广播已经被开发。所有RF电路,包括低噪声放大器,混频器,锁相环,一个压控振荡器,和一个中频滤波器成功的在一块芯片上采用low-if集成。

简介:

地面数字广播,被称为数字音频广播(DAB),已经在欧洲引入了使用正交频分复用技术(OFDM)调制方案。相似的地方带宽窄带VHF频段430 kHz的广播服务计划也将于2003年在日本推出。由于个人发展和便携式接收机是对广播服务被广泛渗透到市场中必不可少的。

数字广播在传统的超外差收音机情况下,中频(IF)的接收选择为相对高的频率来拒绝图像

信号,一个外部SAW滤波器,需要为选择滤波器来拒绝相邻的信号。这是接收机具有许多RF电路的主要原因,因此导致了大的功率消耗。另一方面,基于集成在芯片信道选择滤波器的单芯片射频前端用于基于便携式模拟AM / FM广播接收器的发展已经被报道,已实现RF前端系统的更小的尺寸和更低的功耗。

在欧洲和日本,地面数字声音广播频道将被分配到现有强模拟电视信号之间的未被使用的通道。因此,在数字声音广播所需的相邻信道抑制比已经比在传统的FM无线电接收机需要高得多。因此精确的频率选择和在半导体工艺变化过程中的高精度在集成IF滤波器的设计中被强烈要求。为了满足中频滤波器的选择性要求,许多中方法被研究,例如:在使用具有外部调整功能的当前的可变电阻的方法;半导体变化过程中在带通滤波器调整当前震荡器频率来补偿中心频率的便宜。与那些在模拟广播接收机中使用比较,也有在数字声音广播中使用的多载波系统如OFDM,需要本地振荡器,以提供较低的相位噪声性能。

本文实现单芯片射频前端的地面数字声音录制广播,展示如以下几项:

(1)RF前端架构

(2)新技术

(3)总体特性

RF前端架构

为了实现由个人便携接收机所要求的小尺寸RF前端和低功耗的要求,该RF前端IC已经被开发,利用了BiCMOS技术7GHz的双极型和1 UM-CMOS晶体管。接收器的系统配置包括这种单芯片射频前端和数字基带处理器。

在一般情况下,数字基带处理LSI的功耗可以用半导体工艺技术的进步降低即使在电路的结构没有改变的情况下,但这种方式不一定对于模拟电路能够实现。因此,需要新的RF前端系统结构的发展,以显著降低功耗的模拟电路。

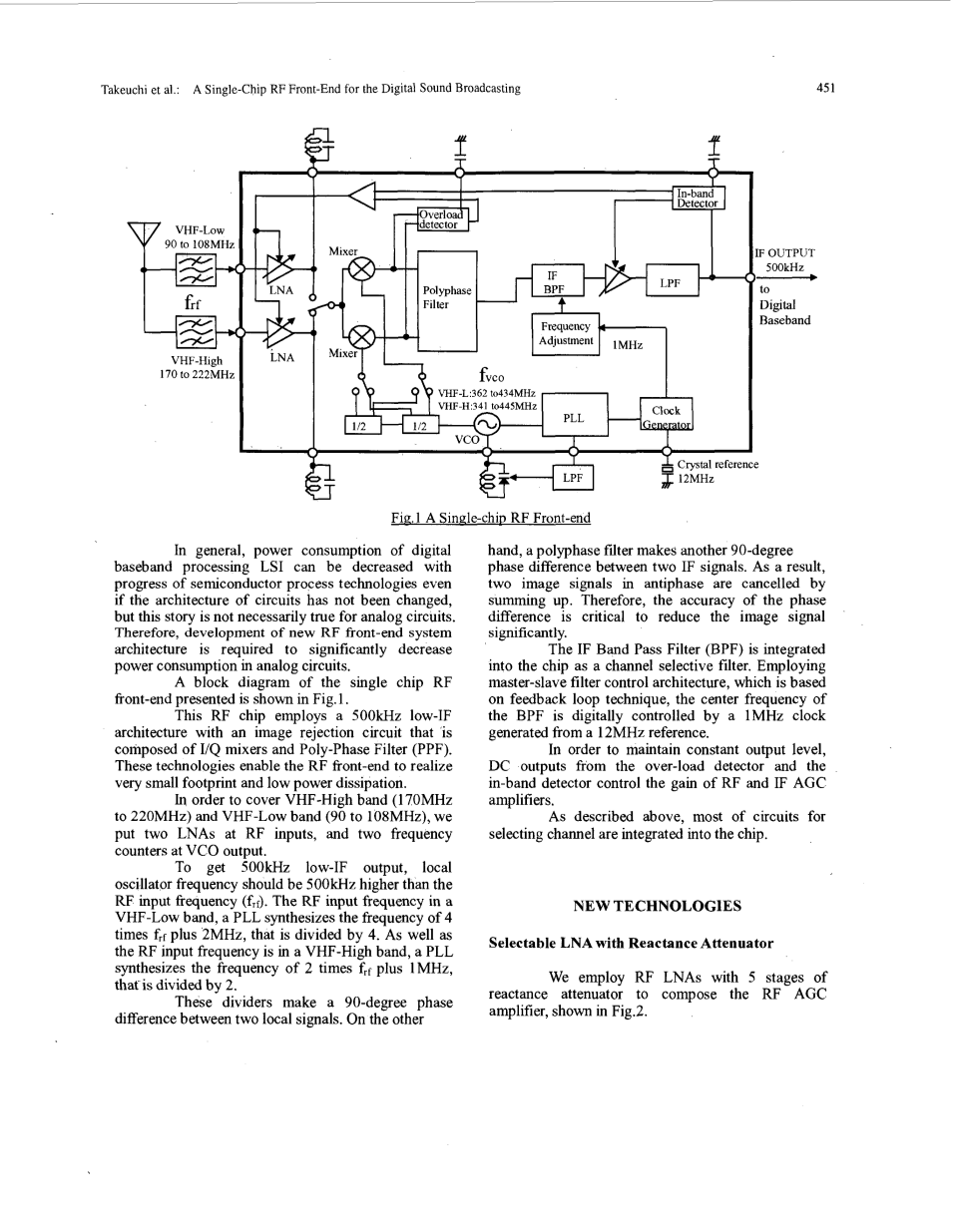

单芯片RF射频前端的框图如图一所示

图1.单芯片射频前端

该射频芯片采用500 kHz的由I / Q混频器和多相滤波器(PPF)的图像抑制电路组成的低中频架构。这些技术使射频前端实现占用小空间和低功耗。

为了覆盖VHF-高频段(170 MHz的至220兆赫)和VHF低频带(90〜108MHz),我们在RF输入两个LNA,在VCO输出两个频率计数器。

为了获得500kHz的低IF输出,本地振荡频率应该比RF输入频率(FRF)高500千赫,在VHF-低频段的RF输入频率,一个PLL合成的4次F,F加上2MHz的频率,即除以4。若RF输入频率是在一个VHF到高频段,一个PLL合成的2倍的频率F,F加上1兆赫,即除以2。

这些分压器使两个本地信号之间产生90度相位差。另一方面,多相滤波器使得两个IF之间产生另一个90度的相位差信号。其结果是,在反相两个图像信号互相抵消,所以相位差的精度对显著降低图像信号而言至关重要。

IF带通滤波器(BPF)被集成到芯片作为沟道选择性滤波器。用主从滤波器控制结构,它是基于反馈环路技术,在BPF的中心频率被LMHz时钟控制,在BPF的中心频率被数字从12 MHz参考产生的LMHz时钟数字化控制。

为了保持恒定的输出电平,过负荷检测器和带内检测器的DC输出控制RF和IF AGC放大器的增益。

如上所述,大多数用于选择信道的电路都集成到芯片。

新技术

选择低噪声放大器电抗衰减器

我们采用射频LNA与电抗衰减器的5个阶段来组成的RF AGC放大器,如图2所示。

每级提供大约8分贝衰减,其结果是超过50分贝的动态范围仅在RF级得到的。该电路的总增益可以通过低噪音变化器的交换持续改变,如图3所示的特性曲线。

一般情况下,电阻会产生相当大的噪声。这就是我们采用电抗衰减器而不是电阻衰减器来实现低噪声特性的原因。

I / Q混频器

图像抑制结构由两个相同的混频器实现频率变化,每个混频器由NPN吉尔伯特单元,PNP电流镜像电路和缓冲放大器组成。为了显著降低图像信号,VQ混合器输出之间的相位差需要是精确的90度。这就是I / Q混频需要在电路设计和布局设计方面相同的原因。

锁相环(PLL)电路由以设计ECL(射极耦合逻辑)的电路32/33双模预分频器,CMOS变频柜,相位比较器和电荷泵组成。环路滤波器,调谐变容二极管和VCO的LC槽的部件是片外。

这种震荡器采用差动拍手振荡器包括可以产生顺从本地输出到二极管的负荷反馈电容器的振荡器。通常情况下,能够同时接收的VHF到高和VHF-低波段,需要两个本地振荡器,但是,这种RF芯片已与两个简单的计数器来实现它在一个单一的振荡器。与VHF到高带的90度相位差的两个本地信号从1/2频率计数器的输出产生,并且那些用于VHF-低频段是在两个级联1/2频率计数器的输出得到的。

多相滤波器(PPF)

集成滤波器的电路结构示于图4。

这种滤波器由五个阶段R-C网络的,提供了在各截止频率的90度相移。这种PPF已经通过保持从200千赫到1MHz的90度相移使得图像抑制比(IMRR)大于60分贝。多项滤波器和图象抑制性能的相移特性的仿真结果示于图5和图6。

IF带通滤波器(BPF)

一个集成IF带通滤波器(BPF)使用10阶双二阶滤波器,如图7所示。带通滤波器使用的运算放大器具有300 MHz的带宽。BPF呈现拥有低损失和陡峭边缘选择性的600KH在的通带。

它通过串联加入芯片上的低通滤波器已达到的总的相邻信道干扰抑制比60dB以上。IF带通滤波器的频率响应的模拟结果示于图8。

BPF的中心频率是由主从滤波器控制结构固定到500kHz来取消频率偏移,在接下来的部分中描述。

主从滤波器控制架构

图9展示了主从滤波器控制结构图。12MHz的参考晶振除以12产生1MHz参考时钟,1MHz参考时钟的低通滤波的输出在模拟相位比较器被进行比较。所述MHz参考时钟和其过滤的输出之间的相位差被由5位控制信号的相位比较器保持为90度,所以它允许修复主LPF和从BPF的截止频率。

图10示出了主低通滤波器电路。在该电路中,电阻比确定Q因子,科罗的时间常数确定截止频率。因此,在该过滤器的组件的布局设计结构可能会影响元件的价值,必须极其小心进行。主站和从站过滤器的可变电阻(RI,R2,R3和R4)可以由FET的5位控制信号开关从32个不同的值来选择的电阻值,如图11所示。

以这种方式,采用具有精心设计布置的反馈回路技术,低通滤波器呈现稳定Q值和稳定的截止频率特性,不依赖于半导体工艺的变化。

总体特性

在这一节中,我们描述实际的测量结果。为了忽略外部滤波器的影响,RF输入从天线输入只通过宽频带巴伦不带天线滤波器注入该芯片。从测量结果看,该芯片允许射频输入范围从-100dBm到-10dBm, 维持输出的OdBm状态保持小于1分贝偏差,并显示出非常低的IM3的值,如低于-55dBc在-1dB平方米色调天线输入,在图12所示。

图13示出了图像抑制性能.从90 MHz到108MHz的和170MHz的到222MHz所有频率范围内,可以获得高于40分贝IMRRs。这种性能有利于整个信道的频率选择性的反馈,特别是在 1兆赫调谐频率偏移的情况下。

从天线输入总体频率选择性响应从IF输出图入图14所示。全方位呈现了陡峭的10阶切比雪夫活跃BPF,反应了1.2MHz的截止LPF和镜像抑制。该图显示显著镇压值。例如,在-930kHz60dB以上偏移量,即这种频率下其中模拟TV声音载波可能被分配,90dB以上偏移量为 1.53MHz,其中的模拟电视视频载波可能被分配的频率,以及超过lOOdB偏移的频率为 /-3MHz。

典型的相位噪声以及其频率特性示于图15和图16所示。190MHz偏移1KHz的相位噪声值低于-8OdBc/赫兹,并随着频率升高逐渐增加。但在最高频率,相位噪声仍然低至-79dBc/ Hz的,相位误差从200Hz到1kHz的整合为0.56deg。

此3V BIOS芯片接收机的总功耗是大约100mW。

在3V接收机的总体特征总结在表1中,评估电路板如图17所示。这些性能可满足其中16 QAM或QPSK将被用作调制方案以达到数字声音广播服务的要求。

该RF芯片具有9平方毫米芯片面积,其显微照片如图18所示。

|

输入频率 |

90MHz to 108MHz and 170MHz to 222MHz |

|

输入动态范围 |

大于90分贝 /-1分贝输出偏差 |

|

输出频率 |

500KHz |

|

双音互调三阶产物输出 |

~-55dBc@190MHz-1 OdBm 2-tone input |

|

镜像抑制比 |

﹥40dB |

|

NF |

4.4dB@l90MHz |

|

相位噪声 |

-81dBC/Hz@190MHz,1KHz偏差 |

|

相位误差 |

0.5deg(200Hz-100kHz偏差)@190KHz |

|

能量消耗 |

100mW/ 3Vdc |

|

芯片尺寸 |

3.03mm*3.03mm |

|

包装 |

40-pinQFP:9mm*9mm |

表1

结论:

采用具有镜像抑制电路的低中频结构,一个用于数字声音广播的完整的单芯片RE已经在BiCMOS工艺用小尺寸来实现。该芯片包括电抗衰减器,I / Q混频器低噪声放大器,锁相环,压控振荡器,一个PPF和中频滤波器控制中心频率,表现出色而功耗仅为在3V的样子。它非常适合用于具有小尺寸,低功耗和低成本的便携数字广播。

感谢

作者要感谢给N.Shirota(S&S架构中心),M.Toyoshima(无线电信实验室),K.山际(半导体网络公司),STanemo(索尼白石半导体),M.Takeda(半导体网络公司)和S&S交流和S.N.C.,SONY公司为他们在该芯片的发展援助和合作的东西。

参考文献

[1]M.Uehara, M.Takada, T.Kuroda“传输方案对地面ISDB系统”消费电子,第45卷,1期,1999年2月,pp.101-106 ,IEEE交易

[2] M.Bolle,D.Clawin,K.Gieseke“接收器引擎芯片组的数字音频广播信号系统与电子技术”

1998年ISP98国际研讨会于1998URSI发表,pp.388-342

[3] W.Titus R.Groughwel1等“一个实现DAB目的的硅BJT RF双频接收机IC”1998年IEEE MTT-S文摘,pp.345-348

[4] M.Goldfarb,R.Groughwel1等“用于DAB的Si BJT IF下变频器/ AGC IC”1998年IEEE MTT-S文摘,pp.353-356

[5] T.Okonoboh.Tomiyama“一个先进的低功耗无线单芯片IC”于电子IEEE交易,卷40,4号,1994年11月,pp.842-851

[6] T.Okanobu, H.To

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[31291],资料为PDF文档或Word文档,PDF文档可免费转换为Word